中国黄金集团j建设公司网站郑州网站关键词推广

程序设计=数据结构+算法

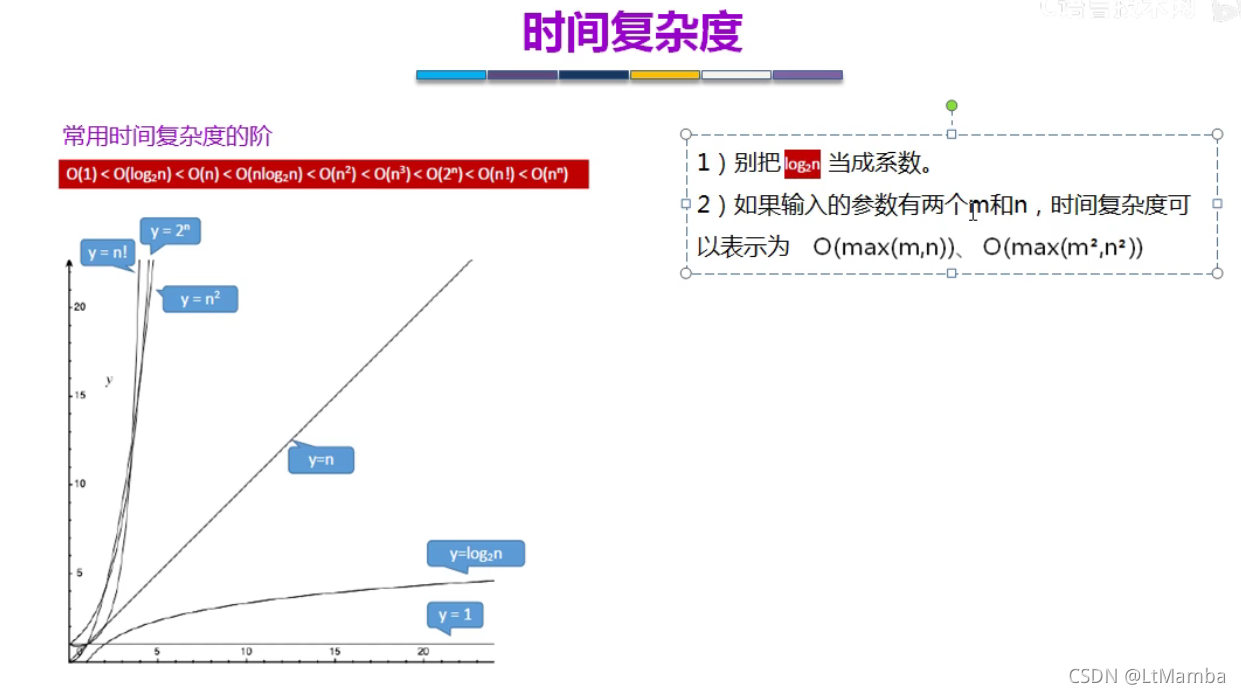

只谈数据结构不谈算法就跟去话剧院看梁山伯与祝英台结果只有梁山伯在演,祝英台生病了没来一样。

本文的所有内容都出自《大话数据结构》这本书中的代码实现部分,建议看书,书中比我本文写的全。

数据结构,直白地理解,就是研究数据的存储方式。

1. 数据结构–概念

数据结构是一门研究非数值计算的程序设计问题中的操作对象,以及它们之间的关系和操作等相关问题的学科。

1.1 基础概念

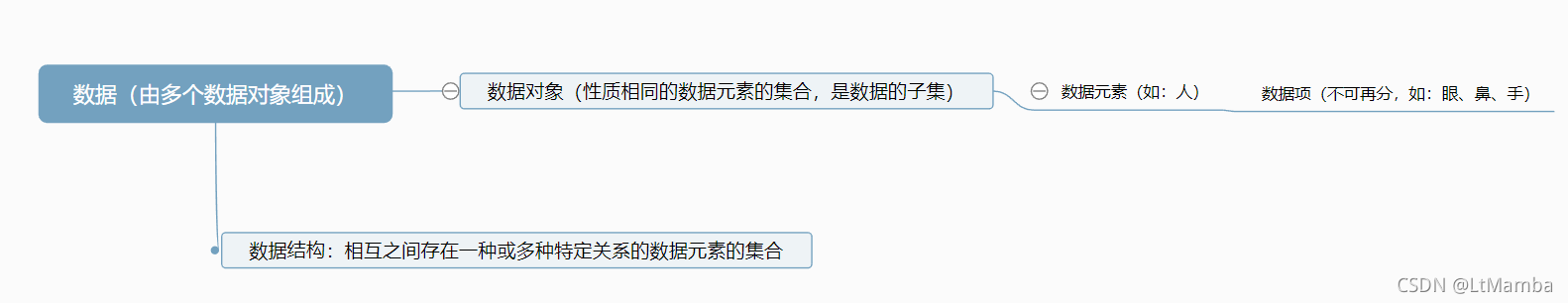

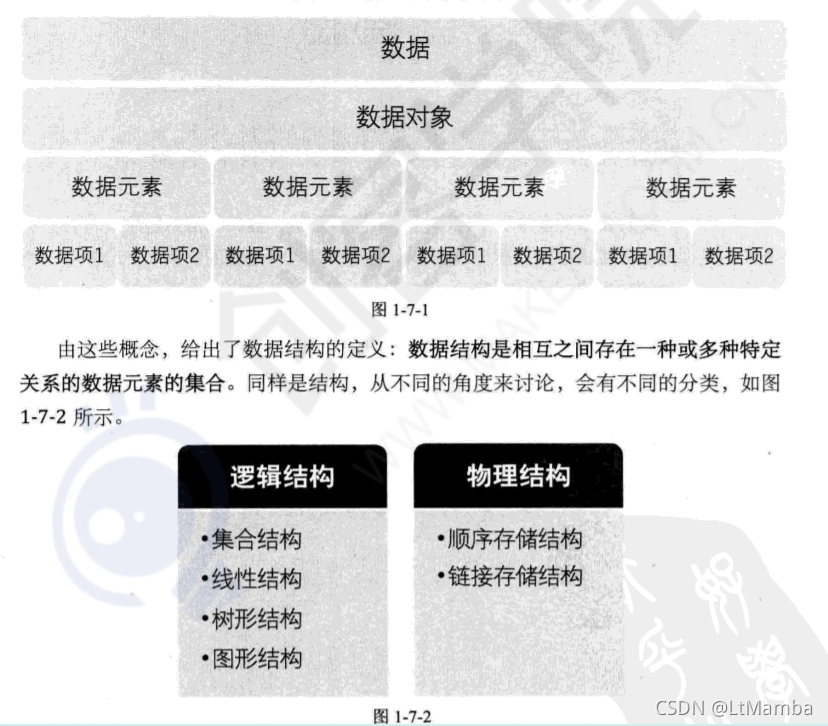

1.2 数据结构分类

什么是数据结构?

数据对象在**计算机中的组织方式**数据对象必定与一系列加在其上的操作相关联

完成这些操作所用的方法就是算法

1.2.1 线性结构–一对一

又称 线性表。

具备“一对一”关系的数据就可以使用线性表来存储。线性表并不是一种具体的存储结构,包括: 1. 顺序存储结构(简称顺序表)2. 链式存储结构(简称链表或单链表)3. 特殊的线性表:栈 和 队列数据分散的存储在物理空间中,通过一根线保存着它们之间的逻辑关系,这种存储结构称为*链式存储结构(简称链表)*

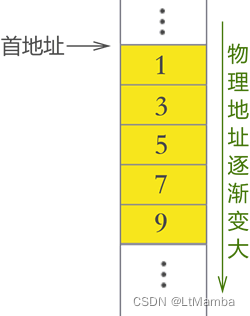

1.2.1.1 顺序存储结构(简称顺序表)

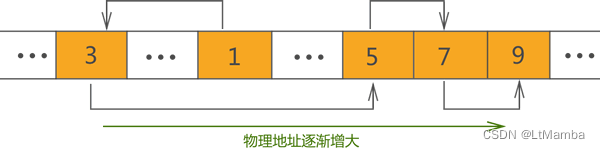

将数据依次存储在连续的整块物理空间中,这种存储结构称为*顺序存储结构(简称顺序表)*顺序表,不能简单理解为 语言中的数组,因为数组只是语言中实现线性表的其中一种表现形式。顺序表存储数据时,会提前申请一整块足够大小的物理空间,然后将数据依次存储起来,物理存储是连续的。顺序表的实现借助的语言中的 数组(因为数组申请的是连续的空间)。

顺序表结构如下:

1.2.1.2 链式存储结构(简称链表或单链表)

使用链表存储数据时,是随用随申请,因此数据的存储位置是相互分离的。数据元素随机存储,并通过指针表示数据之间逻辑关系的存储结构就是链式存储结构链表不限制数据的物理存储状态,换句话说,使用链表存储的数据元素,其物理存储位置是随机的。

1.2.1.3 栈

栈和队列隶属于线性表,是特殊的线性表。

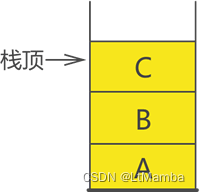

栈是一种只能从表的一端存取数据且遵循 "先进后出" 原则的线性存储结构。实现:既可以利用顺序存储结构实现,又可以利用练市链式存储结构实现。

栈的c语言实现包括

-

顺序栈

借用数组实现 -

链式栈

借用链表实现

1.2.1.4 队列

栈和队列隶属于线性表,是特殊的线性表。

先进先出。实现:既可以利用顺序存储结构实现,又可以利用练市链式存储结构实现。

1.2.1.5 串存储结构

串存储结构也是一种线性存储结构,因为字符串中的字符之间也具有"一对一"的逻辑关系。串结构只用于存储字符类型的数据。串实现:1. 定长顺序存储,即普通数组(又称静态数组)存储。2. 堆分配存储:用动态数组存储字符串;3. 块链存储:用链表存储字符串;

1.2.1.6 广义表(又称列表)

参考链接

广义表一般采用链式存储实现,因为根据广义表中元素分析使用数组实现会造成空间浪费。

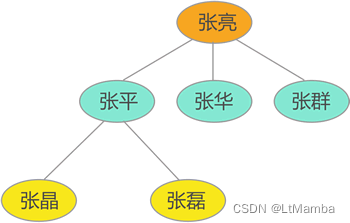

1.2.2 树–一对多

存储结构适合存储具有“一对多”关系的数据。

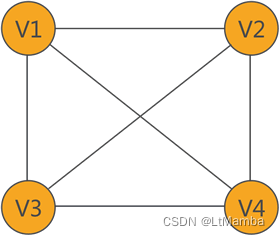

1.2.3 图–多对多

图存储结构适合存储具有“多对多”关系的数据。

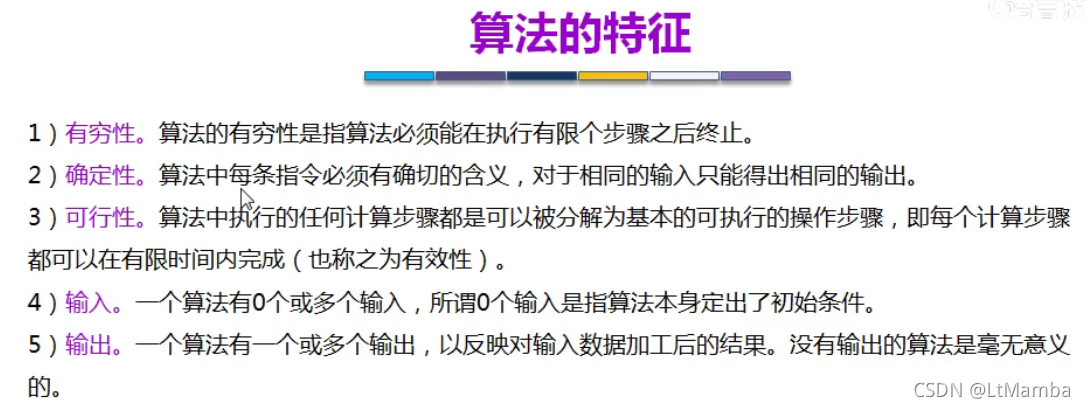

2. 算法–概念

2.1 算法基础概念

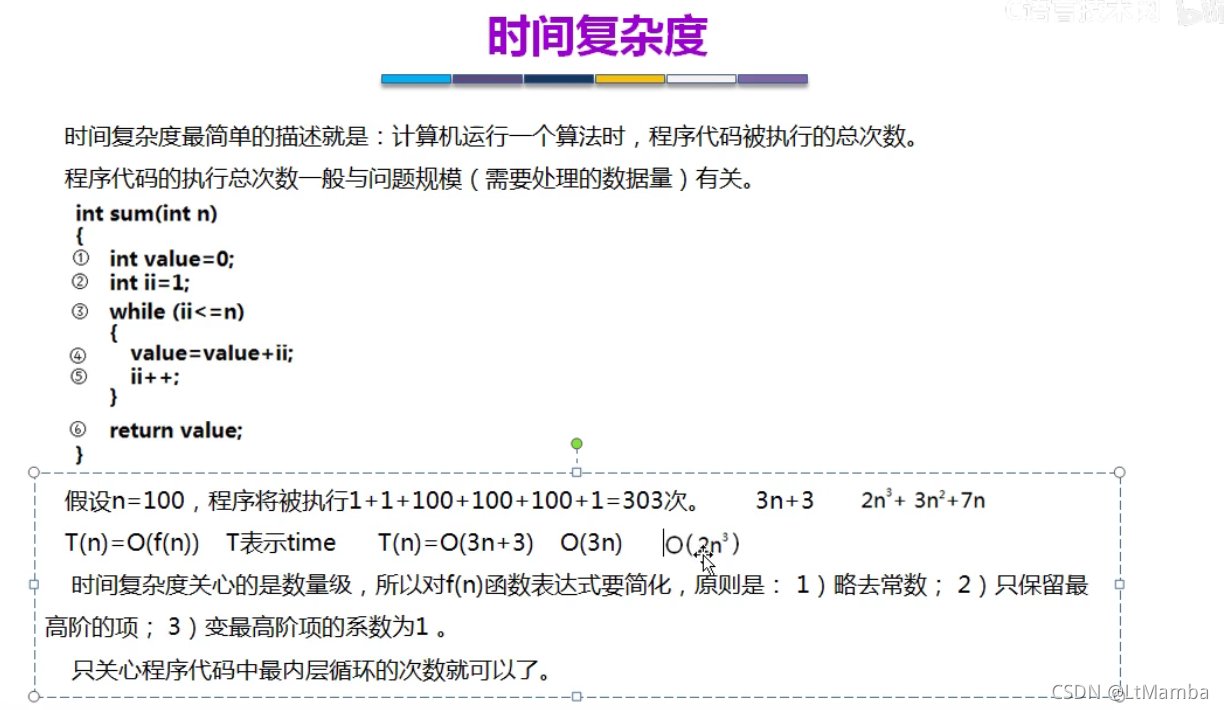

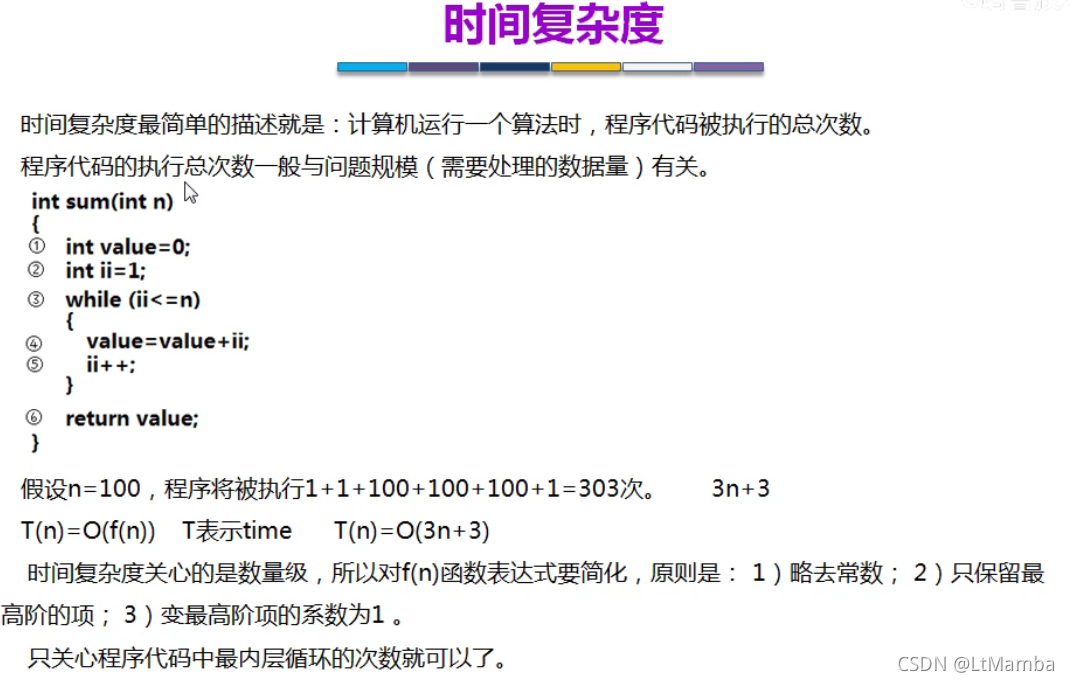

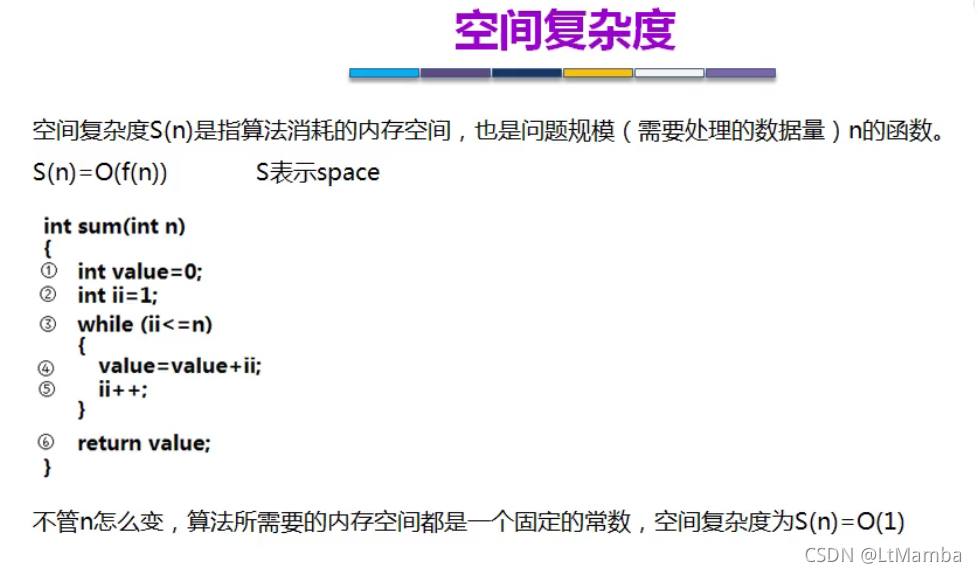

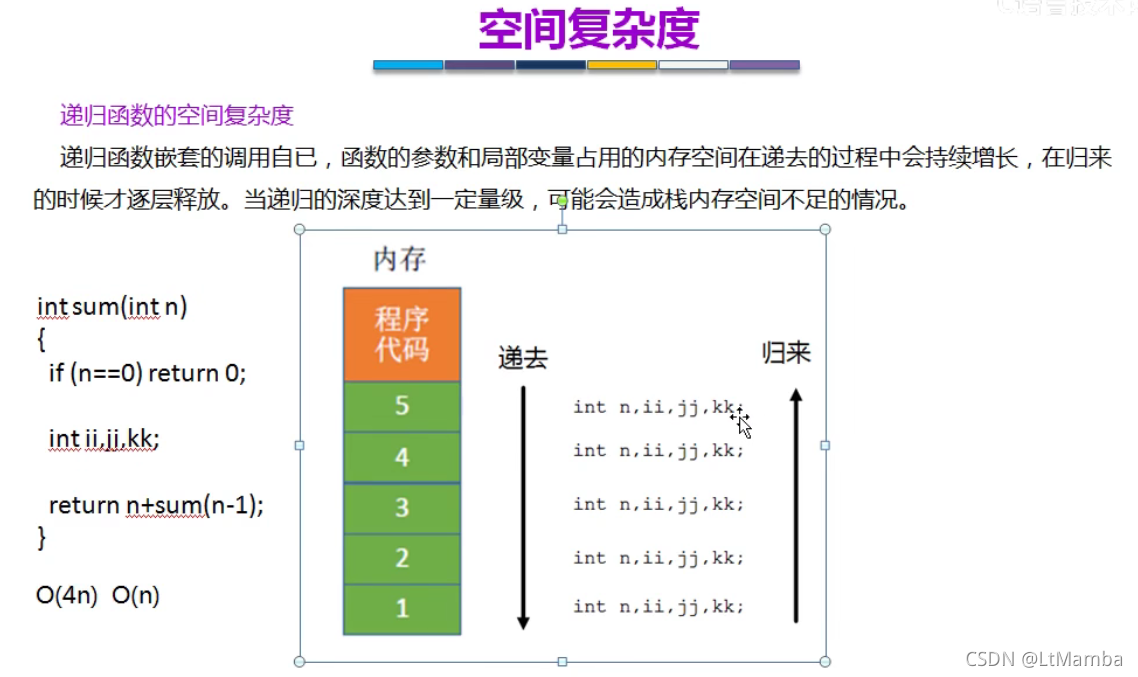

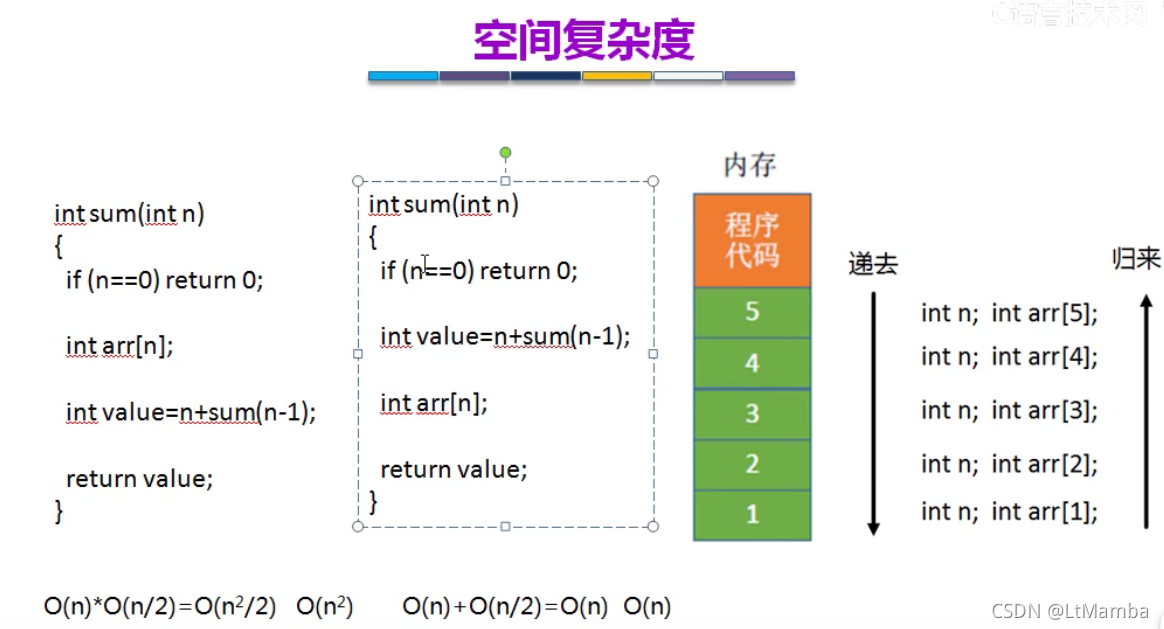

2.2 算法效率评估